nrf24l01+p+lna 1100 esp8266

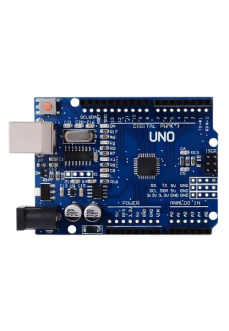

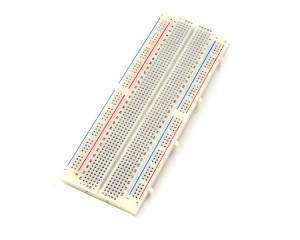

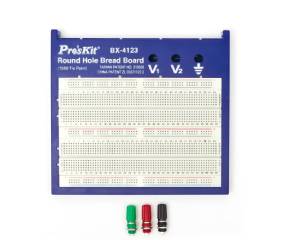

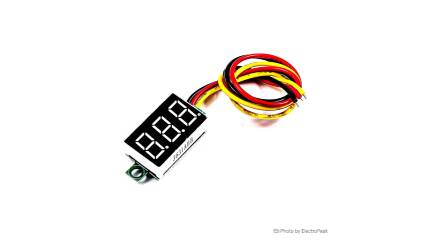

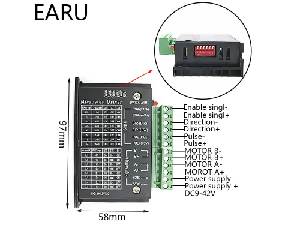

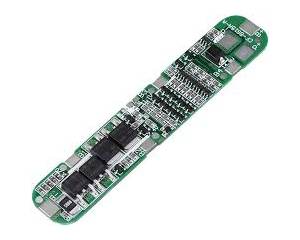

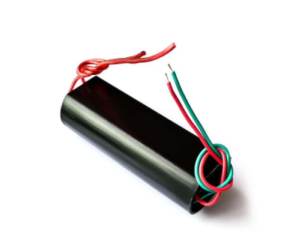

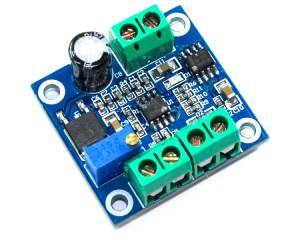

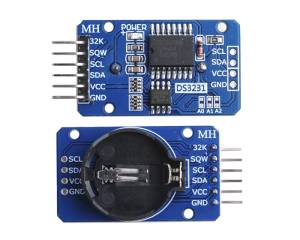

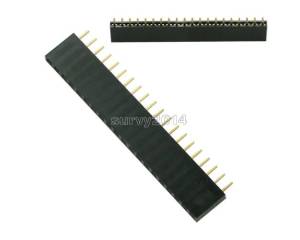

Arduino components

Availablity In stock

5 JOD

4 JOD

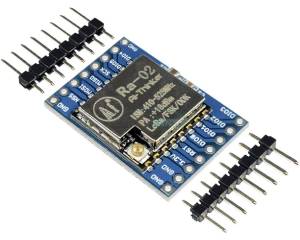

ESP8266 - ESP8266EX - Serial Interface Wi-Fi Module - ESP-01

Corresponding Interface:

SDIO 2.0, SPI, UART

32-pin QFN package

Integrated RF switch, balun, 24dBm PA, DCXO, and PMU

Integrated RISC processor, on-chip memory and external memory interfaces

Integrated MAC/baseband processors

Quality of Service management

I2S interface for high fidelity audio applications

On-chip low-dropout linear regulators for all internal supplies

Proprietary spurious-free clock generation architecture

Integrated WEP, TKIP, AES, and WAPI engines

Specification:

802.11 b/g/n

Wi-Fi Direct (P2P), soft-AP

Integrated TCP/IP protocol stack

Integrated TR switch, balun, LNA, power amplifier and matching network

Integrated PLLs, regulators, DCXO and power management units

+19.5dBm output power in 802.11b mode

Power down leakage current of <10uA

Integrated low power 32-bit CPU could be used as application processor

SDIO 1.1/2.0, SPI, UART

STBC, 1×1 MIMO, 2×1 MIMO

A-MPDU & A-MSDU aggregation & 0.4ms guard interval

Wake up and transmit packets in < 2ms

Standby power consumption of < 1.0mW (DTIM3)

21022024030510.jpg)

21022024030510.jpg)

17022024104156.jpg)

17022024104507.jpg)

17022024105339.jpg)

17022024110013.jpg)

18022024063201.jpg)

18022024064305.jpg)

18022024064708.jpg)

18022024065402.jpg)

19022024120531.jpg)

19022024121208.jpg)

19022024121652.jpg)

19022024122157.jpg)

19022024123002.jpg)

19022024123231.jpg)

19022024123728.jpg)

19022024124038.jpg)

19022024124546.jpg)

19022024125201.jpg)

19022024125730.jpg)

19022024053303.jpg)

19022024053620.jpg)

19022024053837.jpg)

19022024054334.jpg)

05082024082134.jpg)

19022024055146.jpg)

19022024055459.jpg)

19022024055824.jpg)

19022024060939.jpg)

19022024061247.jpg)

19022024063548.jpg)

19022024065145.jpg)

19022024070435.jpg)

19022024071308.jpg)

19022024071706.jpg)

19022024072154.jpg)

19022024072713.jpg)

19022024074822.jpg)

19022024113040.jpg)

19022024113846.jpg)

22112025031114.jpg)

20022024123336.jpg)

20022024123824.jpg)

20022024124752.jpg)

20022024125347.jpg)

20022024020749.jpg)

20022024021008.jpg)

20022024012756.jpg)

20022024013310.jpg)

20022024020410.jpg)

20022024021837.jpg)

20022024045700.jpg)

20022024052358.jpg)

20022024053156.jpg)

21022024031239.jpg)

21022024032705.jpg)

21022024033753.jpg)

21022024035040.jpg)

21022024071551.jpg)

21022024072233.jpg)

21022024073153.jpg)

21022024074213.jpg)

21022024074709.jpg)

21022024075116.jpg)

21022024080047.jpg)

13062024122756.jpg)

22052024113502.jpg)

13052024012418.jpg)

13052024012645.jpg)

13052024012817.jpg)

13052024013117.jpg)

13052024015056.jpg)

15052024023852.jpg)

25122025025654.jpg)

21052024050334.jpg)

21052024052051.jpg)

22052024114515.jpg)

22052024115243.jpg)

22052024115609.jpg)

23052024030600.jpg)

23052024031037.jpg)

23052024031441.jpg)

23052024032529.jpg)

23052024052247.jpg)

25052024010441.jpg)

25052024012158.jpg)

25052024012635.jpg)

25052024014608.jpg)

25052024015422.jpg)

25052024015736.jpg)

25052024020252.jpg)

25052024020410.jpg)

25052024020622.jpg)

25052024020731.jpg)

25052024020842.jpg)

24062024120829.jpg)

13122024113957.jpg)

29112024114727.jpg)

11122024041134.jpg)

11122024062005.jpg)

16122024054422.jpg)

16122024055059.jpg)

28122024123528.jpg)

28122024124728.jpg)

15012025040845.jpg)

16102025033558.jpg)

16102025040145.jpg)

01112025053910.jpg)

08112025034317.jpg)

16112025112009.jpg)

19112025034432.jpg)

22112025030626.jpg)

22112025031405.jpg)

22112025035500.jpg)

22112025035737.jpg)

01122025054806.jpg)

02122025044654.jpg)

11122025045759.jpg)

06012026122527.jpg)

12012026034217.jpg)

17012026111410.jpg)