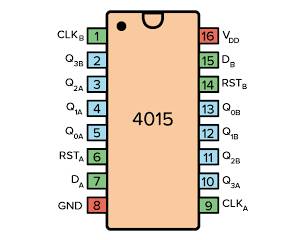

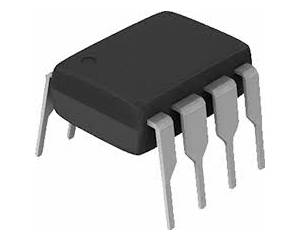

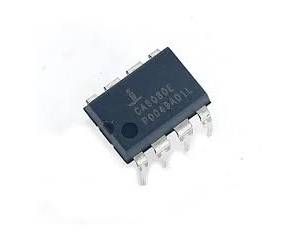

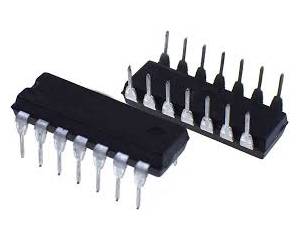

IC CD4015

Electronics components

Availablity In stock

2 JOD

1 JOD

CD4015BE CD4015 CD4015 CMOS Dual 4-Stage Static Shift Register Breadboard-Friendly IC DIP-16

Dual 4-Stage Static Shift Register

CD4015 Features:

Dual 4-stage static shift register: Two independent 4-bit shift registers.

Parallel and serial input/output: Flexible data transfer.

High-speed operation: Clock frequency: 10 MHz.

Low power consumption: Maximum 80 μA.

Wide operating range: 4.5V to 15.5V.

Compatibility: TTL (Transistor-Transistor Logic) and CMOS (Complementary Metal-Oxide-Semiconductor).

High output drive capability: 24 mA sink, 16 mA source.

Pinout (16-pin DIP/SOIC/TSSOP):

Inputs:

CLK (Clock) - Pin 1: Clock input for both shift registers.

PARALLEL DATA IN (P0-P3) - Pins 2-5: Parallel input for shift register 1.

PARALLEL DATA IN (P4-P7) - Pins 6-9: Parallel input for shift register 2.

SERIAL DATA IN (SI) - Pin 10: Serial input for both shift registers.

Outputs:

PARALLEL DATA OUT (Q0-Q3) - Pins 11-14: Parallel output for shift register 1.

PARALLEL DATA OUT (Q4-Q7) - Pins 15-16 and 2-5: Parallel output for shift register 2.

SERIAL DATA OUT (SO) - Pin 10: Serial output for both shift registers.

Power:

Vcc (Pin 16): Positive power supply.

GND (Pin 8): Ground.

Applications:

Data storage and transfer: Shift register applications.

Digital displays: Display drivers for LEDs or LCDs.

Sequencers: Control and automation.

Frequency dividers: Clock division.

Digital counters: Event counting.

Electrical Characteristics:

Clock frequency: 10 MHz.

Input voltage range: 0V to Vcc.

Output voltage swing: 0V to Vcc - 0.5V.

Propagation delay: 10-30 ns.

Power dissipation: 80 μA per stage

28052024051550.jpg)

26052024034656.jpg)

08052024041021.jpg)

08052024041210.jpg)

08052024041343.jpg)

08052024041624.jpg)

08052024041827.jpg)

08052024042006.jpg)

08052024042148.jpg)

08052024042704.jpg)

08052024050512.jpg)

08052024050701.jpg)

08052024051728.jpg)

08052024063522.jpg)

08052024063753.jpg)

08052024064138.jpg)

11052024010009.jpg)

11052024010307.jpg)

11052024010501.jpg)

11052024010633.jpg)

11052024010822.jpg)

11052024010955.jpg)

11052024011159.jpg)

11052024011611.jpg)

11052024012638.jpg)

11052024012836.jpg)

11052024013037.jpg)

12052024050410.jpg)

12052024050901.jpg)

12052024051211.jpg)

12052024051857.jpg)

12052024052644.jpg)

12052024053212.jpg)

12052024054654.jpg)

13052024015628.jpg)

13052024015846.jpg)

13052024020042.jpg)

13052024020416.jpg)

13052024020624.jpg)

13052024020744.jpg)

13052024024812.jpg)

13052024025808.jpg)

13052024030141.jpg)

13052024030928.jpg)

13052024032015.jpg)

13052024032343.jpg)

13052024032951.jpg)

13052024033249.jpg)

13052024033603.jpg)

13052024033933.jpg)

13052024034204.jpg)

13052024034813.jpg)

15052024032420.jpg)

15052024032639.jpg)

15052024032842.jpg)

15052024033034.jpg)

15052024033356.jpg)

15052024033559.jpg)

15052024055200.jpg)

15052024055457.jpg)

15052024055855.jpg)

15052024060116.jpg)

15052024060319.jpg)

15052024061043.jpg)

15052024061201.jpg)

15052024061326.jpg)

15052024061702.jpg)

15052024061856.jpg)

15052024062124.jpg)

15052024063619.jpg)

15052024063818.jpg)

15052024064238.jpg)

15052024064610.jpg)

15052024064844.jpg)

15052024065352.jpg)

15052024065532.jpg)

15052024065711.jpg)

15052024065931.jpg)

15052024070204.jpg)

19052024031838.jpg)

19052024032051.jpg)

19052024032458.jpg)

19052024032700.jpg)

19052024033136.jpg)

19052024033533.jpg)

19052024040251.jpg)

19052024041155.jpg)

19052024041424.jpg)

19052024041701.jpg)

19052024044437.jpg)

19052024044725.jpg)

19052024045056.jpg)

19052024045303.jpg)

19052024050327.jpg)

19052024064441.jpg)

19052024064842.jpg)

19052024065253.jpg)

19052024065637.jpg)

19052024065947.jpg)

19052024070420.jpg)

19052024070754.jpg)

19052024071103.jpg)

19052024071530.jpg)

21052024010046.jpg)

21052024010238.jpg)

21052024010609.jpg)

21052024010810.jpg)

21052024011048.jpg)

21052024011301.jpg)

21052024015942.jpg)

21052024020135.jpg)

21052024020356.jpg)

21052024021015.jpg)

21052024021417.jpg)

21052024021752.jpg)

22052024033731.jpg)

22052024034111.jpg)

22052024034257.jpg)

22052024034718.jpg)

22052024035113.jpg)

22052024040112.jpg)

26052024031229.jpg)

26052024031705.jpg)

26052024032056.jpg)

26052024032345.jpg)

26052024032917.jpg)

26052024033604.jpg)

26052024034202.jpg)

26052024034910.jpg)

26052024035349.jpg)

26052024035540.jpg)

26052024035751.jpg)

26052024040227.jpg)

26052024040610.jpg)

26052024040802.jpg)

26052024041944.jpg)

26052024042200.jpg)

26052024042418.jpg)

26052024042620.jpg)

26052024043340.jpg)

26052024043534.jpg)

26052024043800.jpg)

26052024044008.jpg)

26052024044206.jpg)

26052024045724.jpg)

26052024045946.jpg)

26052024050155.jpg)

26052024050511.jpg)

26052024050705.jpg)

26052024050856.jpg)

26052024051247.jpg)

26052024051709.jpg)

26052024051905.jpg)

27052024023113.jpg)

27052024024503.jpg)

27052024025032.jpg)

27052024025701.jpg)

27052024030000.jpg)

27052024030318.jpg)

27052024030659.jpg)

27052024031718.jpg)

27052024032300.jpg)

27052024032712.jpg)

27052024033358.jpg)

27052024042509.jpg)

27052024042934.jpg)

27052024052218.jpg)

27052024052612.jpg)

27052024053032.jpg)

27052024053835.jpg)

27052024054453.jpg)

27052024061504.jpg)

27052024062838.jpg)

27052024064036.jpg)

27052024064527.jpg)

27052024064945.jpg)

27052024065516.jpg)

27052024065934.jpg)

27052024070530.jpg)

27052024070900.jpg)

28052024121620.jpg)

28052024121937.jpg)

28052024122257.jpg)

28052024122655.jpg)

28052024123231.jpg)

28052024123730.jpg)

28052024124202.jpg)

28052024124413.jpg)

28052024124629.jpg)

28052024124840.jpg)

28052024125130.jpg)

28052024010057.jpg)

28052024010432.jpg)

28052024010645.jpg)

28052024010929.jpg)

28052024011154.jpg)

28052024011409.jpg)

28052024011636.jpg)

28052024012025.jpg)

28052024012242.jpg)

28052024020652.jpg)

28052024020957.jpg)

28052024021236.jpg)

28052024021616.jpg)

28052024022347.jpg)

28052024032055.jpg)

28052024045905.jpg)

28052024050115.jpg)

28052024050305.jpg)

28052024050534.jpg)

28052024050732.jpg)

28052024051140.jpg)

28052024051342.jpg)

28052024051933.jpg)

28052024052129.jpg)

28052024052329.jpg)

28052024052955.jpg)

28052024053157.jpg)

28052024053407.jpg)

28052024053633.jpg)

28052024054011.jpg)

28052024054744.jpg)

28052024055042.jpg)

30052024124812.jpg)

30052024125127.jpg)

30052024125437.jpg)

30052024125842.jpg)

30052024010035.jpg)

30052024020158.jpg)

30052024020348.jpg)

30052024020843.jpg)

30052024021119.jpg)

30052024021610.jpg)

30052024021824.jpg)

30052024022113.jpg)

30052024022719.jpg)

30052024023000.jpg)

30052024023253.jpg)

30052024023509.jpg)

30052024023738.jpg)

30052024024011.jpg)

30052024024344.jpg)

30052024024529.jpg)

30052024024715.jpg)

30052024025042.jpg)

30052024032353.jpg)

30052024032844.jpg)

30052024033110.jpg)

30052024033256.jpg)

30052024033740.jpg)

30052024033923.jpg)

30052024034208.jpg)

30052024034427.jpg)

30052024035300.jpg)

30052024035413.jpg)

30052024035535.jpg)

30052024035646.jpg)

02062024123424.jpg)

02062024123707.jpg)

02062024124220.jpg)

02062024124627.jpg)

02062024125020.jpg)

02062024125545.jpg)

02062024125737.jpg)

02062024010011.jpg)

02062024010600.jpg)

02062024010854.jpg)

02062024023325.jpg)

02062024024613.jpg)

02062024035847.jpg)

02062024040026.jpg)

02062024040157.jpg)

02062024040322.jpg)

02062024040533.jpg)

02062024040838.jpg)

02062024041052.jpg)

02062024041253.jpg)

02062024041521.jpg)

02062024041703.jpg)

06062024050127.jpg)

06062024050610.jpg)

06062024050613.jpg)

06062024050816.jpg)

06062024050818.jpg)

06062024051007.jpg)

06062024051230.jpg)

06062024051411.jpg)

06062024051544.jpg)

06062024051720.jpg)

06062024051858.jpg)

06062024052040.jpg)

06062024052322.jpg)

06062024052446.jpg)

06062024052615.jpg)

06062024052756.jpg)

06062024052924.jpg)

08062024055100.jpg)

08062024055539.jpg)

08062024060121.jpg)

08062024060308.jpg)

08062024061537.jpg)

08062024061739.jpg)

08062024064301.jpg)

08062024064433.jpg)

08062024064631.jpg)

08062024064901.jpg)

08062024065051.jpg)

08062024065252.jpg)

08062024070014.jpg)

08062024070206.jpg)

08062024070648.jpg)

08062024070820.jpg)

11062024035820.jpg)

11062024035948.jpg)

12062024014542.jpg)

12062024014721.jpg)

12062024014901.jpg)

12062024020234.jpg)

12062024020357.jpg)

12062024020718.jpg)

13062024125131.jpg)

13062024125758.jpg)

13062024125959.jpg)

13062024010252.jpg)

13062024010818.jpg)

13062024011216.jpg)

13062024011431.jpg)

13062024011742.jpg)

13062024011906.jpg)

20062024032017.jpg)

20062024032734.jpg)

20062024033031.jpg)

20062024033337.jpg)

20062024033813.jpg)

20062024034220.jpg)

20062024034522.jpg)

20062024034932.jpg)

20062024035243.jpg)

20062024035827.jpg)

20062024041359.jpg)

20062024041921.jpg)

20062024042232.jpg)

20062024044705.jpg)

22062024042313.jpg)

22062024042515.jpg)

22062024043022.jpg)

22062024043300.jpg)

22062024043637.jpg)

22062024043834.jpg)

22062024044036.jpg)

22062024044326.jpg)

22062024044535.jpg)

22062024044805.jpg)

22062024045007.jpg)

24062024012256.jpg)

24062024012716.jpg)

24062024013159.jpg)

24062024013706.jpg)

24062024013938.jpg)

24062024022220.jpg)

24062024023823.jpg)

24062024024228.jpg)

24062024024450.jpg)

24062024024752.jpg)

24062024024952.jpg)

24062024025152.jpg)

24062024025405.jpg)

24062024025602.jpg)

24062024045442.jpg)

24062024051526.jpg)

24062024051921.jpg)

24062024052120.jpg)

24062024052522.jpg)

24062024053328.jpg)

24062024053615.jpg)

19122024022414.jpg)

11122024071446.jpg)

19122024020138.jpg)

19122024021207.jpg)

19122024051342.jpg)

19122024061937.jpg)

21122024030131.jpg)

21122024031156.jpg)

21122024033820.jpg)

21122024034117.jpg)

21122024035235.jpg)

25112025072155.jpg)

25112025112342.jpg)

18122025063214.jpg)

14012026020803.jpg)